# LAB 3: - DECODERS, DISPLAYS AND MULTIPLEXERS ITI1100 - Digital Systèmes Winter 2024 School of Electrical Engineering and Computer Sciences University of Ottawa

Professeur: Dr. H.T.Mouftah Teaching assistant: Mohammad, Siddhant, Emilia

> Groupe#32 Mohamed Luc Aurel Degnon,30026055 Rahima Daher,300287494

> > Experiment Date :2024-02-(12-26) Soumission Date :2024-03-12

#### **Objective**

- Analyse, construct and test a simple 2-to-4 decoder.

- Construct and test a seven-segment decoder display

- Analyse, construct and test a simple multiplexer.

#### **Equipment and components**

- Quartus II 13.0 Service-Pack 1

- Altera DE2-115 card

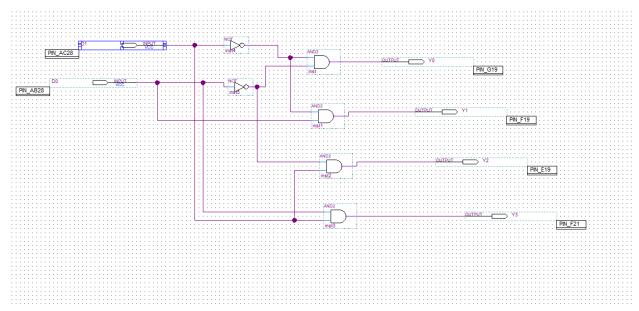

## <u>Circuit Diagrams</u> Part I – A 2-to-4 Decoder

*Figure 1: Screenshot of a circuit diagram of a 2 to 4 decoder (Figure 5.3.2 of the lab manual)*

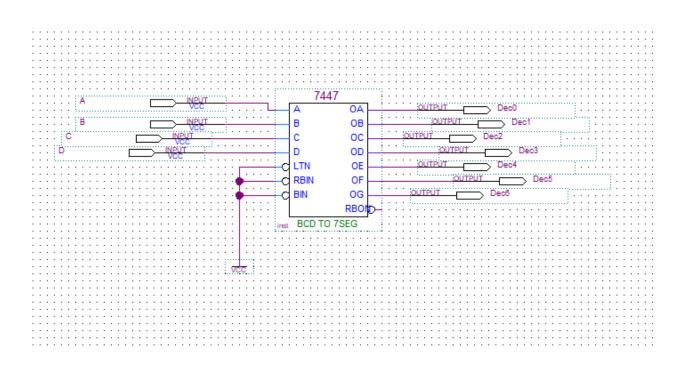

#### **Part II – Decoder and Seven Segment Display**

Figure 2: Screenshot of a circuit diagram of a standard decoder and circuit display for a 7-segment display (Figure 5.3.4 in the lab manual)

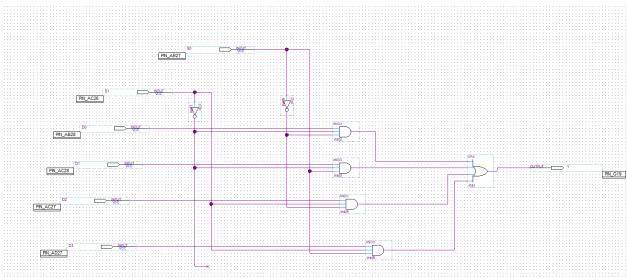

Part III – Multiplexers

*Figure 3: Screenshot of a schematic of a 4-in-1 multiplexer (Figure 5.3.5 in the manual of the laboratory)*

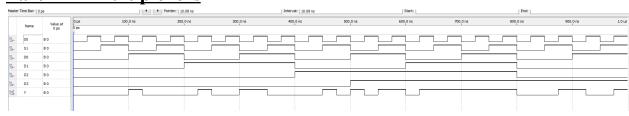

## **Experimental Data and Data Processing** Part I – A 2-to-4 Decoder

| le Ei    | dit View    | Simulation Help  |               |           |           |                     |          |             |          | s        | - D >    |

|----------|-------------|------------------|---------------|-----------|-----------|---------------------|----------|-------------|----------|----------|----------|

|          | ) 🔬 🖞       | ₩ Z XE X         | E SK XE XE XE | 응 양 작 🔤 🐘 |           |                     |          |             |          |          |          |

| laster 1 | Time Bar: 0 | ps               |               | Pointer   | 301.46 ns | Interval: 301.46 ns |          | Start: 0 ps | En       | d: 0 ps  |          |

|          | Name        | Value at<br>0 ps | 0 ps<br>0 ps  | 100.0 ns  | 200.0 ns  | 300,0 ns            | 400.0 ns | 500.0 ns    | 600.0 ns | 700,0 ns | 800.0 ns |

| 5-       | DO          | B 0              | Ľ             |           |           |                     |          |             |          |          |          |

| 5-       | D1          | B 0              |               |           |           |                     |          |             |          |          |          |

| at 🗎     | YO          | B 1              |               |           |           |                     |          | 1           |          |          |          |

| at i     | Y1          | B 0              | 1             |           | 1         |                     |          |             |          |          | ٦        |

| 8        | ¥2          | B 0              |               |           |           |                     |          |             | [        |          |          |

| 3        | Y3          | B 0              |               |           |           |                     |          |             |          |          |          |

|          |             |                  |               |           |           |                     |          |             |          |          |          |

|          |             |                  |               |           |           |                     |          |             |          |          |          |

| Inputs determined<br>from<br>dip switches |       | Observed<br>LED<br>output |                       |                |                |

|-------------------------------------------|-------|---------------------------|-----------------------|----------------|----------------|

| $D_0$                                     | $D_1$ | Y <sub>0</sub>            | <b>Y</b> <sub>1</sub> | Y <sub>2</sub> | Y <sub>3</sub> |

| 0                                         | 0     | 1                         | 0                     | 0              | 0              |

| 0                                         | 1     | 0                         | 1                     | 0              | 0              |

| 1                                         | 0     | 0                         | 0                     | 1              | 0              |

| 1                                         | 1     | 0                         | 0                     | 0              | 1              |

Table 1: Experimental data observed from the circuit board in Figure 1

## <u>Part II – Decoder and Seven Segment Display</u>

|             |           |                  |                         |            |          |                    |          |          |          |          | - 0 ×           |

|-------------|-----------|------------------|-------------------------|------------|----------|--------------------|----------|----------|----------|----------|-----------------|

|             |           | Simulation Help  | o3.sim.vwf (Read-Only)] |            |          |                    |          |          |          | -        |                 |

|             |           |                  |                         |            |          |                    |          |          |          | 56       | arch altera.com |

|             |           |                  | 88 XC XX XX XB 142 4    |            |          |                    |          |          |          |          |                 |

| Master      | Time Bar: | ) ps             |                         | Pointer: 2 | i1.65 ns | Interval: 261.65 n |          | Start:   | End      | ÷ [      |                 |

|             |           |                  |                         | 100.0 ns   | 200,0 ns | 300.0 ns           | 400.0 ns | 500.0 ns | 600.0 ns | 700.0 ns | 800.0 ns ^      |

|             | Name      | Value at<br>0 ps | 0 ps                    |            |          |                    |          |          |          |          |                 |

| in_         | A         | 80               |                         |            |          |                    |          |          |          |          |                 |

| 13-         | 8         | 80               |                         |            |          |                    |          |          |          |          |                 |

| 13-         | с         | 80               |                         |            |          |                    |          |          |          |          |                 |

| <u>is</u> _ | D         | 80               |                         |            |          |                    |          |          |          |          |                 |

| 앮           | Dec0      | B 0              |                         |            |          |                    |          |          |          |          |                 |

| 25          | Dec1      | B 0              |                         |            |          |                    |          |          |          |          |                 |

| 95          | Dec2      | 80               |                         |            |          |                    |          |          |          |          |                 |

| 95          | Dec3      | 80               |                         |            |          |                    |          |          |          |          |                 |

| 25          | Dec4      | 80               |                         |            |          |                    |          |          |          |          |                 |

| 25          | Dec5      | 80               |                         |            |          |                    |          |          |          |          |                 |

| 25          | Dec6      | B 1              |                         |            |          |                    |          |          |          |          |                 |

| Inputs |   |   |   | Outputs        |                |                |                |                |                       |                |

|--------|---|---|---|----------------|----------------|----------------|----------------|----------------|-----------------------|----------------|

| Α      | B | С | D | D <sub>0</sub> | $\mathbf{D}_1$ | D <sub>2</sub> | D <sub>3</sub> | $\mathbf{D}_4$ | <b>D</b> <sub>5</sub> | D <sub>6</sub> |

| 0      | 0 | 0 | 0 | 0              | 0              | 0              | 0              | 0              | 0                     | 1              |

| 0      | 0 | 0 | 1 | 1              | 0              | 0              | 1              | 1              | 1                     | 1              |

| 0      | 0 | 1 | 0 | 0              | 0              | 1              | 0              | 0              | 1                     | 0              |

| 0      | 0 | 1 | 1 | 0              | 0              | 0              | 0              | 1              | 1                     | 0              |

| 0      | 1 | 0 | 0 | 1              | 0              | 0              | 1              | 1              | 0                     | 0              |

| 0      | 0 | 1 | 0 | 0              | 1              | 0              | 0              | 1              | 0                     | 0              |

| 0      | 1 | 1 | 0 | 0              | 1              | 0              | 0              | 0              | 0                     | 0              |

| 0      | 1 | 1 | 1 | 0              | 0              | 0              | 1              | 1              | 1                     | 1              |

| 1      | 0 | 0 | 0 | 0              | 0              | 0              | 0              | 0              | 0                     | 0              |

| 1      | 0 | 0 | 1 | 0              | 0              | 0              | 0              | 1              | 0                     | 0              |

Table 2: Experimental data observed from the circuit board in Figure 2

#### Part III – Multiplexers

| Inputs                 |                |                |                       |                       |                       |                              |

|------------------------|----------------|----------------|-----------------------|-----------------------|-----------------------|------------------------------|

| determined<br>from DIP |                |                |                       |                       |                       | Observed output              |

| switches               |                |                |                       |                       |                       | Observed output<br>odthe LED |

| S <sub>0</sub>         | S <sub>1</sub> | D <sub>0</sub> | <b>D</b> <sub>1</sub> | <b>D</b> <sub>2</sub> | <b>D</b> <sub>3</sub> | Y                            |

| 0                      | 0              | 0              | X                     | X                     | x                     | 0                            |

| 0 | 0 | 1 | X | X | X | 1 |

|---|---|---|---|---|---|---|

| 0 | 1 | X | 0 | X | x | 0 |

| 0 | 1 | X | 1 | X | x | 1 |

| 1 | 0 | X | X | 0 | x | 0 |

| 1 | 0 | X | X | 1 | x | 1 |

| 1 | 1 | X | X | X | 0 | 0 |

| 1 | 1 | X | X | X | 1 | 1 |

Table 3: Experimental data observed from the PCB in Figure 3

## **Comparison of Theoretical Data and Experimental Data** <u>Part I – A 2-to-4 Decoder</u>

Table 1-2 : Comparison of Theoretical and Experimental results from *circuitdiagram of a 2 to 4 decoder*

| Inputs         | _     | Expected<br>Results |                |   |                | Actual<br>Results |                |                |                |

|----------------|-------|---------------------|----------------|---|----------------|-------------------|----------------|----------------|----------------|

| $\mathbf{D}_0$ | $D_1$ | Y <sub>0</sub>      | $\mathbf{Y}_1$ | Y | Y <sub>3</sub> | Y <sub>0</sub>    | $\mathbf{Y}_1$ | Y <sub>2</sub> | Y <sub>3</sub> |

|                |       |                     |                | 2 |                |                   |                |                |                |

| 0              | 0     | 1                   | 0              | 0 | 0              | 1                 | 0              | 0              | 0              |

| 0              | 1     | 0                   | 1              | 0 | 0              | 0                 | 1              | 0              | 0              |

| 1              | 0     | 0                   | 0              | 1 | 0              | 0                 | 0              | 1              | 0              |

| 1              | 1     | 0                   | 0              | 0 | 1              | 0                 | 0              | 0              | 1              |

The results observed experimentally for a circuit of a 2 to 4 decoder were identical to the results obtained theoretically as expected

#### <u>Part II – Decoder and Seven Segment Display</u>

Table 5: Comparison of theoretical and experimental results for a circuit logic using two types of gates

| Inputs |   |   |   | Expecte<br>d<br>Results | _      |                |        |        |                       |                | Expecte<br>d<br>Results |        |        |        |        |       |        |

|--------|---|---|---|-------------------------|--------|----------------|--------|--------|-----------------------|----------------|-------------------------|--------|--------|--------|--------|-------|--------|

| Α      | B | C | D | $\mathbf{D}_{0}$        | D      | $\mathbf{D}_2$ | D      | D      | <b>D</b> <sub>5</sub> | D <sub>6</sub> | D <sub>0</sub>          | D      | D      | D      | D      | $D_5$ | D      |

| 0      | 0 | 0 | 0 | 0                       | 1<br>0 | 0              | 3<br>0 | 4<br>0 | 0                     | 1              | 0                       | 1<br>0 | 2<br>0 | 3<br>0 | 4<br>0 | 0     | 6<br>1 |

| 0      | 0 | 0 | 1 | 1                       | 0      | 0              | 1      | 1      | 1                     | 1              | 1                       | 0      | 0      | 1      | 1      | 1     | 1      |

| 0      | 0 | 1 | 0 | 0                       | 0      | 1              | 0      | 0      | 1                     | 0              | 0                       | 0      | 1      | 0      | 0      | 1     | 0      |

| 0      | 0 | 1 | 1 | 0                       | 0      | 0              | 0      | 1      | 1                     | 0              | 0                       | 0      | 0      | 0      | 1      | 1     | 0      |

| 0      | 1 | 0 | 0 | 1                       | 0      | 0              | 1      | 1      | 0                     | 0              | 1                       | 0      | 0      | 1      | 1      | 0     | 0      |

| 0      | 0 | 1 | 0 | 0                       | 1      | 0              | 0      | 1      | 0                     | 0              | 0                       | 1      | 0      | 0      | 1      | 0     | 0      |

| 0      | 1 | 1 | 0 | 0                       | 1      | 0              | 0      | 0      | 0                     | 0              | 0                       | 1      | 0      | 0      | 0      | 0     | 0      |

| 0      | 1 | 1 | 1 | 0                       | 0      | 0              | 1      | 1      | 1                     | 1              | 0                       | 0      | 0      | 1      | 1      | 1     | 1      |

| 1      | 0 | 0 | 0 | 0                       | 0      | 0              | 0      | 0      | 0                     | 0              | 0                       | 0      | 0      | 0      | 0      | 0     | 0      |

| 1      | 0 | 0 | 1 | 0                       | 0      | 0              | 0      | 1      | 0                     | 0              | 0                       | 0      | 0      | 0      | 1      | 0     | 0      |

The results observed experimentally for a circuit two types of gates were identical to the results obtained theoretically as expected

| Table 5.3.1: Disp | lay corresponding | to 0-9 digits |

|-------------------|-------------------|---------------|

|                   |                   | •             |

| $D_3D_2D_1D_0$ | Correspondin<br>g Display | $D_3D_2D_1D_0$ | Correspondin<br>g Display |

|----------------|---------------------------|----------------|---------------------------|

| 0000           | 0                         | 0001           | 1                         |

| 0010           | 2                         | 0011           | 3                         |

| 0100 | 4 | 0101 | 5 |

|------|---|------|---|

| 0110 | 6 | 0111 | 7 |

| 1000 | 8 | 1001 | 9 |

#### Part III – Multiplexers

Table 6: Comparison of theoretical and experimental results for a circuit logic using a 4-to-1 multiplexer circuit

| Inputs           |                |                |                       |                       |                       | Expected<br>Results | Actual<br>Results |

|------------------|----------------|----------------|-----------------------|-----------------------|-----------------------|---------------------|-------------------|

| $\mathbf{S}_{0}$ | $\mathbf{S}_1$ | D <sub>0</sub> | <b>D</b> <sub>1</sub> | <b>D</b> <sub>2</sub> | <b>D</b> <sub>3</sub> | Y                   | Y                 |

| 0                | 0              | 0              | x                     | x                     | x                     | 0                   | 0                 |

| 0                | 0              | 1              | X                     | X                     | X                     | 1                   | 1                 |

| 0                | 1              | x              | 0                     | X                     | X                     | 0                   | 0                 |

| 0                | 1              | x              | 1                     | X                     | x                     | 1                   | 1                 |

| 1                | 0              | x              | x                     | 0                     | x                     | 0                   | 0                 |

| 1                | 0              | x              | x                     | 1                     | x                     | 1                   | 1                 |

| 1                | 1              | x              | x                     | x                     | 0                     | 0                   | 0                 |

| 1                | 1              | x              | x                     | x                     | 1                     | 1                   | 1                 |

The experimentally observed results for a 4-to-1 multiplexer circuit were identical to the results obtained theoretically as expected

## **Discussion and conclusion:**

Some minor hardware issues have caused a delay in completing the experiment, However, the experiment concluded with an expected results table and completely matching outcomes.Since we have only worked with small LEDs as the output technology so far, it was helpful in to demonstrate the same principles through another output. In particular, the 7-segment display proved to be a useful tool in showcasing numerous applications for binary numbers, as well as circuit patterns and other previously encountered technologies.

The decoder was another application of minimization and simplification. Using two variables to produce four unique results was more efficient than having one result per variable or a similar configuration. The concepts derived from executing this initial experiment can be applied to larger decoders to achieve exponentially larger result pools from relatively few input variables.

The use of the multiplexer explained the almost opposite effect compared to the decoder. Instead of using a number of variables to control even more output variables, the multiplexer was able to utilize switching variables to determine which data variables would affect the final output. In this way, different results could be obtained by considering different variables. In a project setting, this could translate to employing a different method to obtain a variable while still using it for the same result.

This lab demonstrates several ways to utilize variables for controlling one another, for different types of output, and for various output sizes. It serves as a valuable testament to the versatility of utilizing variables in any good system

Appendix (Pré-Lab)

Part (2) 0 11 3 Yo = PI Do ,  $Y_1 = \overline{D_1} D_0$ , Y2= D, Do Y3= P100 Yo Y2 Y3 Do Y2 Do Ya X Y3 Di 0 0 010 6 0 0 11-0-20 6 D when PrDo=1, so the output will always be Xi.

parto : corresponding Display 03 Di PL Do 0 2 3 4 5 01 7 0 0 8 (r 9 0 part 3 " It is 4 to 2 multiplexer. Y= 51 500 + 51 50 D1 + 51 50 D2 + 51 50 D3 V PG D3 Pz Pi 50 51 Y=Do 0 0 0 0 6 0 Y=D, 0 0 YS Dr 1 0 :0 0 ¥=03 0 I

Scanned with CamScanner